Verilog HDL Simulator Technology

Verilog HDL Simulator Technology

ABSTRACT

Digital logic design is becoming increasingly complex in multi-billion transistor VLSI. In order to model such a complex circuit, Verilog has emerged to be one of the most widely used Hardware Description Languages in digital VLSI design. Verilog's ability to model a circuit at different levels makes it a preferred mode of design entry. At every stage in the development, simulations are needed to verify circuit correctness. Various sorts of software and hardware assisted digital logic simulators were developed ever since the adoption of Verilog within the industry. Researchers are actively studying new techniques and approaches to keep simulators relevant. This blog surveys the research activities in Verilog simulator technologies.

What is Verilog Simulation ?

Verilog is a hardware description language and there is no requirement for designers to simulate their RTL designs to be able to convert them into logic gates. So what is the need to simulate?

Simulation is a technique of applying different input stimulus to the design at different times to examine if the RTL code behaves the intended way. Essentially, simulation is a well-followed technique to verify the robustness of the design. It is also the same as how a fabricated chip are going to be utilized in the real world and the way it reacts to different inputs.For example, the design above represents a positive edge detector with inputs clock and signal which are evaluated at periodic intervals to calculate the output pe as shown. Simulation allows us to look at the timing diagram of related signals to know how the design description in Verilog actually behaves.

Free and Open source Simulators

- Cascade

- Just-in-Time Verilog simulator and compiler for FPGAs allowing to instantly run both synthesizable and unsynthesizable Verilog on hardware

- GPL Cver

- This is a GPL open-source simulator. It is a pure simulator. This simulator is not fully IEEE 1364-2001 compliant. It does not support generate and constant functions.

- Icarus Verilog

- Also known as iverilog. Good support for Verilog 2005, including generate statements and constant functions.

- LIFTING

- LIFTING (LIRMM Fault Simulator) is an open-source simulator able to perform both logic and fault simulation for single/multiple stuck-at faults and single event upset (SEU) on digital circuits described in Verilog.

- Verilator

- This is a very high speed open-source simulator that compiles synthesizable Verilog to multithreaded C++/SystemC. Testbench code must be written as synthesiable RTL, or as a C++ or SystemC testbench. Verilator does not support behavioral Verilog syntax for writing Testbenches. For example, there is no support for verilog tasks with # and @ operators for generating behavioral testbench driver code.

References

http://www.synopsys.com/Tools/Verification/hardware-verification/emulation/Pages/zebu-server-asic-emulator.aspx

http://www.veripool.org/wiki/veripool/Verilog_Simulator_Benchmarks

http://www.mentor.com/products/fv/emulation-systems

http://www.bawankule.com/verilogcenter/simspeed.html

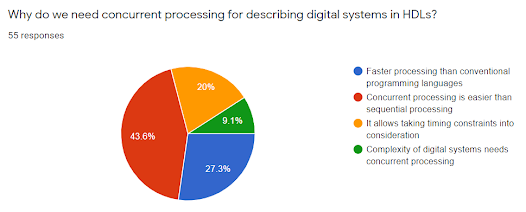

Response Analysis of survey

Thanks, very helpful pful

ReplyDeletevery informative

ReplyDeleteIt was a nice read...

ReplyDeleteIt's nice

ReplyDeleteLooks informative!

ReplyDeleteVery informative

ReplyDeleteNever read such an interesting blog..!

ReplyDeleteGreat work 👍

ReplyDeleteInformative blog

ReplyDeletenice content , great work bro

ReplyDeletevery helpful ,It's a nice read

ReplyDeleteVery well explained.....

ReplyDeletekeep posting such a nice content.

Very well explained.

ReplyDeletekeep posting such content.

I'm not interested in this topic but read it and it is nice

ReplyDelete3rd comment from same account

ReplyDeleteThis comment has been removed by the author.

ReplyDeleteVery well explained.....

ReplyDeletekeep posting such a nice content.

Couldn't have explained it better, well done!!

Very informative. Great job

The blog was very informative and was very crisp. Thank you!!!

Nice article!

Excellent blog.learned new things

nicely written

It was very helpful. Great work!!!

Found it very useful and informative.... Good Work 👍👍

thanks for the appreciation

DeleteInteresting stuff

ReplyDeleteWell done !

ReplyDelete💯💯🤘

ReplyDeleteGood content

ReplyDeleteVery informative thanks for sharing the blog it's really helpful

ReplyDeleteprovides am good introduction to the world of digital design

ReplyDeletethank you bro

DeleteMast

ReplyDeleteSundar😂

ReplyDeleteJalwa🔥

ReplyDeleteAb bass ....😂

ReplyDeleteKya mast banayela hai

ReplyDeleteGreat blog

ReplyDeleteNever thought biology would be this much interesting, great work!!

ReplyDeleteVery nice

ReplyDeleteGood layout and perfect explanation

ReplyDeletethanks a lot

DeleteVery Informative!

ReplyDeleteMast

ReplyDeleteZhakass🔥

ReplyDeleteAb aur blog maat likh bass hogaya😑😂

ReplyDeleteThank you for a nice insight on Verilog simulators!

ReplyDeleteMy friend found this article/blog useful and came to know about nice alternative softwares!

thank you

DeleteSuper...😊

ReplyDelete