Verilog HDL Simulator

Verilog HDL Simulator

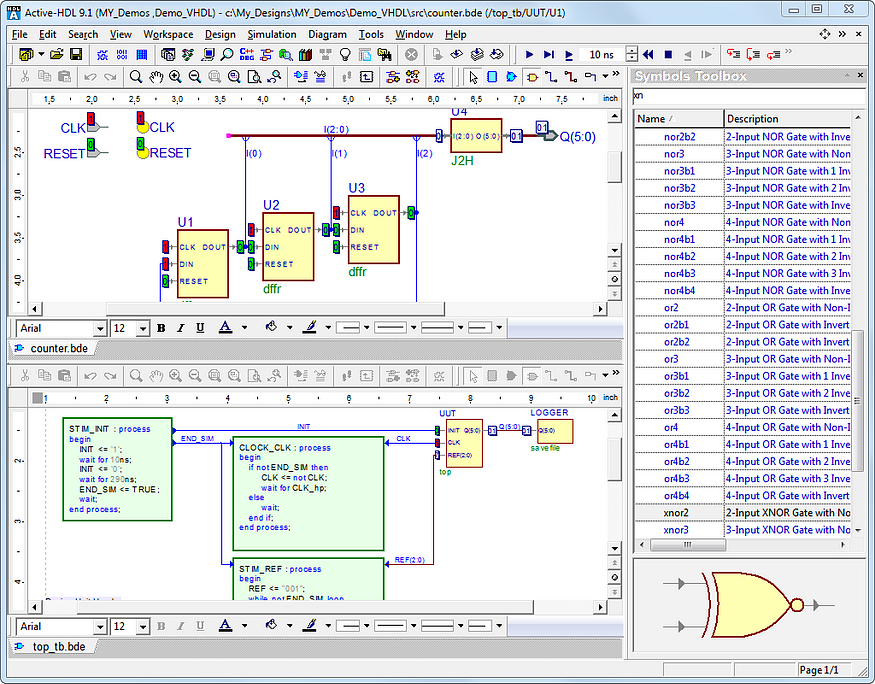

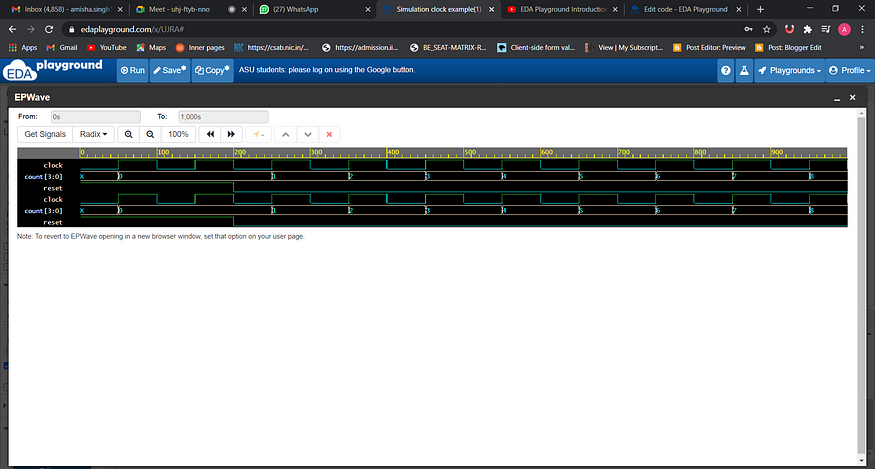

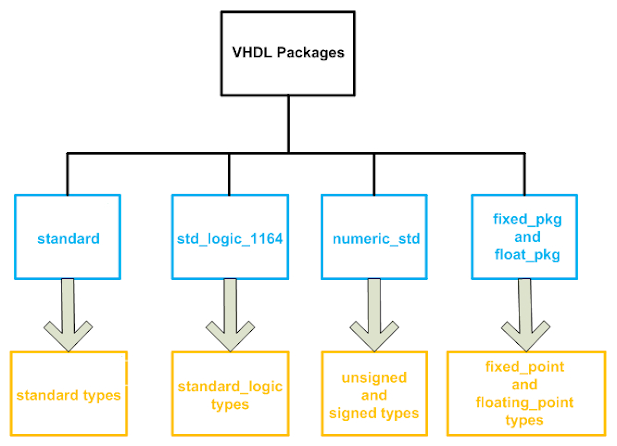

HDL simulation software is also a long way from where it started as a single marketing product offered by one company. Today, simulators are available from many vendors at a variety of prices, including free ones. For desktop / personal use, Aldec, Mentor, LogicSim, SynaptiCAD, TarangEDA and others offer less than US $ 5000 tools on the Windows 2000 / XP platform. The suites integrate the simulator engine with a complete development environment: text editor, waveform viewer, and RTL level browser. In addition, limited Aldec and ModelSim simulator programs are downloaded for free, from OEM partners (Microsemi, Altera, Lattice Semiconductor, Xilinx, etc.) for those who wish open source software, there is Icarus Verilog, GHDL among others.

In addition to the desktop level, enterprise-level simulations offer faster simulation time, stronger language simulation support (VHDL and Verilog), and most importantly, more accurate gate-level simulation (SDF-annotated). The last point is very important in the ASIC tapeout process, where the design database is released in the construction. (Semiconductor Foundries places the use of selected tools on the approved list, so that the customer’s configuration determines the login status. hundreds of entry levels include Cadence Incisive Enterprise Simulator, Mentor ModelSim / SE, and Synopsys VCS. Prices are not publicly published, but all three retailers charge $ 25,000- $ 100,000 USD per seat, a 1 year long-term license.

FPGA vendors do not need expensive business simulators for their design flow. In fact, many retailers are installing the OEM version of a third-party HDL simulator in their design suite. The integrated simulator is taken from the entry or low-level version, and integrated with the FPGA vendor device libraries. For high-volume FPGA projects, an independent simulator is recommended, as the OEM version may not have the capacity or speed to successfully handle large formats.

For more content please read the following article:

https://amisha-singh18.medium.com/verilog-hdl-simulator-aae3544e673b

Much Beneficial Information 👍

ReplyDeleteQuite Informative 💯

ReplyDeleteGreat insight!!

ReplyDeleteNyc

ReplyDeleteamazing knowledge and content on verilog, i would recommend you to give more blogs on such technologies

ReplyDeletethanks for your appreciation bro

DeleteThank you so much

DeletePerfect Simulation

ReplyDeleteYou've set a benchmark of blogging...!

ReplyDeletethanks machha

Delete👌✌️

ReplyDeleteGreat!!!

ReplyDeleteWaiting For More such blogs.....

ReplyDeleteGreat work!

ReplyDeleteInteresting...👍🏻

ReplyDeletevery well explained!

ReplyDeleteNice Explaination 🙌

ReplyDeleteVery informative

ReplyDeleteNice blog!

ReplyDeleteGood content.....great work 👍🏻

ReplyDeleteVery well written!

ReplyDeleteGood info

ReplyDeleteWell done guys... keep posting on this topic

ReplyDeletethanks mate

DeleteAwesome blog and well written! Good job! 👍🏻

ReplyDeleteVery interesting

ReplyDeleteInformative one💯

ReplyDeleteGood content !!

ReplyDeleteVaah, swaad hi aa gaya

ReplyDeleteVery edifying...loved it,

ReplyDeleteInformative Content and very well presented!

ReplyDeletethank you so much

DeleteGreat👍👍👍👍👍👍👍

ReplyDeleteGreat!

ReplyDeleteNice work

ReplyDeleteGreat

ReplyDeleteGood

ReplyDeleteA nice insight on Veriloog simulator!

ReplyDeleteVery informative, nice content,good work

ReplyDeleteWow, awesome information

ReplyDeleteCleared with Concept✌️

ReplyDeleteVery Informative!💯

ReplyDeleteWorth Reading

ReplyDeleteVery Nice Content 💯💯

ReplyDeleteKeep Sharing such Blogs

ReplyDeleteFirst Blog I have ever read😅

ReplyDeletethank you so much

DeleteMuch Deeper

ReplyDeleteBit Interesting

ReplyDeleteAppreciated one💯

ReplyDeleteGood

ReplyDelete🙌🙌🙌

ReplyDeleteGreat Work!!!

ReplyDeleteGreat work 💯

ReplyDeleteVery well expalined!! and well researched

ReplyDeleteGreat work 💯

ReplyDeleteGreat work 💯

ReplyDeleteInformative!

ReplyDeleteInformative 👍

ReplyDeleteGreat work!

ReplyDeleteVery informative 👍

ReplyDeleteInformative 👍👍

ReplyDeleteVery informative 👍

ReplyDeleteVery informative and well explained✌

ReplyDeleteNice 🔥🔥👍

ReplyDeleteGood content!!

ReplyDeleteGreat work !keep it up !

ReplyDeleteGreat work !keep it up !

ReplyDeleteGreat work !keep it up !

ReplyDeleteInformative content

ReplyDeleteWell written and presented!

ReplyDeleteWell written and presented!

ReplyDeleteWell written and presented!

ReplyDeleteInteresting , Keep it up

ReplyDeleteInteresting , Keep it up

ReplyDeleteInformative.

ReplyDeleteGreat Work.. Very Informative 👍

ReplyDeleteGreat content , highly informative!!

ReplyDeleteGreat work

ReplyDeleteInformative

ReplyDeleteGreat work !

ReplyDeleteThere was a lot to learn... Nice Blog💯

ReplyDeleteVery informative!!

ReplyDeleteNice👍👍

ReplyDeleteNice👍👍

ReplyDeleteNice👍👍

ReplyDeleteGreat work

ReplyDeleteGreat Content, Very Informative.

ReplyDeleteWorth a Read !! Great Share.

ReplyDeleteWorth a Read !! Great Share.

ReplyDeleteWorth a Read !! Great Share.

ReplyDeleteVery informative!! Keep writing this type of blogs.

ReplyDelete